| 06.01.2020 [19:29],

Андрей Созинов Компания Micron объявила о начале производства тестовых образцов регистровых модулей оперативной памяти DDR5 RDIMM, которые предназначены для использования в серверах. Первыми образцы новых модулей серверной памяти получат ключевые партнёры компании Micron.  Модули памяти Micron DDR5 RDIMM построены на микросхемах 10-нм класса (1Znm). По словам производителя, они способны обеспечить прирост производительности подсистемы памяти более чем на 85 % по сравнению с актуальными модулями DDR4. При этом они смогут потреблять меньше энергии за счёт уменьшения рабочего напряжения с 1,2 до 1,1 В. Кроме того, новые модули смогут предложить больший объём за счёт увеличения ёмкости самих микросхем.  Компания Micron пока что не стала уточнять, когда планирует начать массовое производство регистровых модулей оперативной памяти DDR5. Вероятнее всего, случится это к 2021 году, когда должны появиться первые процессоры с поддержкой DDR5. О планах выпустить такие процессоры для серверных систем заявила компания Intel (Sapphire Rapids), а также китайская Zhaoxin. Вероятнее всего, компания AMD также не останется в стороне. Также в 2021 году можно ожидать появления памяти DDR5 в настольных системах. 13.12.2019 [08:03], Андрей СозиновЛетом этого года китайская компания Zhaoxin начала поставки своих x86-совместимых 16-нм процессоров KX-6000 для настольных систем и серверных процессоров KH-30000. Теперь же Zhaoxin работает над новыми процессорами, которые придут им на смену.  Новые серверные процессоры KH-40000 китайская компания планирует выпустить в 2021 году. Как и актуальные KH-30000, новинки будут производиться по 16-нм техпроцессу на мощностях TSMC, но получат ряд архитектурных улучшений. Также планируется увеличить максимальное число ядер с нынешних восьми до тридцати двух. В результате компания сможет предложить до 64 ядер на двухпроцессорную систему. Сообщается, что KH-40000 продолжат использовать память DDR4 и интерфейс PCIe 3.0. Также Zhaoxin начала работу над новыми мобильными и настольными процессорами серии KX-7000. Данные процессоры будут производиться уже по 7-нм техпроцессу, а для некоторых из них и вовсе будет использоваться 5-нм техпроцесс. Переход на более «тонкие» техпроцессы позволит компании повысить тактовые частоты своих процессоров, за счёт чего они смогут лучше конкурировать с чипами Intel и AMD.  Сообщается, что в серии процессоров KX-7000 будут присутствовать модели с некой новой интегрированной графикой, совместимой с DirectX 12. Также платформа для новых чипов сможет похвастаться поддержкой интерфейса PCIe 4.0 и оперативной памяти DDR5. К сожалению, конкретные сроки выхода процессоров KX-7000 компания Zhaoxin пока что не уточняет. 25.06.2019 [10:24], Алексей РазинНе так давно представители AMD признались, что задуматься об отказе от разъёма Socket AM4 в настольном сегменте их заставит только какое-то очень серьёзное нововведение. При этом поддержку PCI Express 4.0 компания уже реализовала для Socket AM4, а поддержку этого процессорного разъёма она обязуется осуществлять до 2020 года включительно. По сути, самым вероятным кандидатом на звание «убийцы Socket AM4» может стать поддержка памяти типа DDR5.  Это предположение частично находит поддержку в словах старшего вице-президента AMD Форреста Норрода (Forrest Norrod), который в компании отвечает за развитие серверных платформ. Выдержки из интервью с ним ресурс AnandTech уже публиковал ранее, и это позволило нам узнать, что носителями архитектуры Zen 4 станут серверные процессоры семейства Genoa, но теперь американские коллеги выложили полную версию этого интервью, и она не обошлась без сюрпризов. Норрод заявил, что процессоры Milan с архитектурой Zen 3 будут представлены к середине 2020 года, и они сохранят как поддержку памяти типа DDR4, так и конструктивное исполнение Socket SP3. Для реализации поддержки памяти типа DDR5 серверные платформы компании будут вынуждены перейти на новый тип процессорного разъёма, как поясняет старший вице-президент AMD. Случится ли это с выходом процессоров с архитектурой Zen 4, в разработке которых компания уже продвинулась достаточно далеко, не уточняется. 29.01.2019 [00:17], Илья ГавриченковТехнологии динамической памяти продолжают своё развитие. Несмотря на то, что появление DDR5 SDRAM ожидается лишь в 2020 году, некоторое время тому назад компания SK Hynix, занимающее место второго по величине производителя DRAM, приступила к разработкам следующего поколения перспективной памяти, DDR6 SDRAM. Как ожидается, такая память сможет обеспечить достижение скоростей до 12 Гбит/c на контакт. Но не стоит ждать быстрых перемен: как утверждают представители SK Hynix, разработка будет завершена в лучшем случае в течение ближайших 5–6 лет.  Более того, пока у разработчиков даже нет единого мнения о том, какую архитектуру должна получить память следующего за DDR5 поколения. «Мы обсуждаем несколько концепций пост-DDR5. Одна из них заключается в поддержании нынешней тенденции увеличения скорости передачи данных, а другая — в объединении технологий DRAM с технологиями систем на чипе», — рассказал Ким Донг-Кюн (Kim Dong-kyun), научный сотрудник по разработке DRAM в SK Hynix. Напомним, в конце 2018 года SK Hynix объявила о завершении разработки первых чипов DDR5 SDRAM, которые работают на эффективной частоте 5200 МГц при напряжении 1,1 В. Таким образом, 16-гигабитные чипы DDR5 смогут предложить на первом этапе скорость на уровне 5,2 Гбит/с на контакт, что примерно на 60 % выше пропускной способности, обеспечиваемой DDR4 SDRAM текущего поколения. Но и это не предел, к 2022 году SK Hynix планирует довести эффективную частоту чипов DDR5 до 6400 МГц. Главная сложность в разработке DDR5 касается необходимости понизить зашумлённость полезного сигнала во время высокоскоростной передачи данных. Для решения этой проблемы внедрена технология многофазной синхронизации, а также улучшения протоколов коррекции ошибок. Ожидается, что к 2022 году чипы DDR5 SDRAM будут занимать порядка 45 % рынка.  В то же время принятие DDR6 SDRAM заведомо окажется гораздо более сложным процессом. С этим типом DRAM могут быть связаны серьёзные изменения архитектуры всей подсистемы памяти, поэтому и разработка, и последующее распространение DDR6 будет протекать заметно медленнее, чем в случае с DDR5. Кроме того, индустрия пока не пришла к единому мнению относительно того, что конкретно должна представлять собой DDR6. Иными словами, следующее за DDR5 поколение памяти представляется достаточно туманной перспективой, и сроки её появления могут отодвинуться далеко за 2024 год. 15.11.2018 [15:11], Геннадий ДетиничКомпания SK Hynix — второй в мире по величине производитель памяти типа DRAM — сообщила о разработке 16-Гбит кристаллов DRAM DDR5 с использованием второго поколения техпроцесса класса 10 нм (1Ynm). Это тот же самый новейший техпроцесс компании, с помощью которого она начинает производство 8-Гбит кристаллов DDR4. Забегая вперёд, отметим, что к производству памяти DDR5 компания SK Hynix приступит только в 2020 году, поскольку данный стандарт DRAM пока ещё не принят комитетом JEDEC и не поддерживается разработчиками контроллеров и процессоров. Это лишь заготовка на будущее, которая ждёт своего часа.  Согласно прогнозу аналитиков компании IDC, например, спрос на DDR5 начнёт появляться только в 2020 году, что обещает довести в 2021 году долю DDR5 в мировом объёме производства памяти до 25 % и до 44 % в 2022 году. Поэтому компании SK Hynix, как и остальным лидерам рынка DRAM, не нужно спешить с внедрением в производство этого поколения памяти. Но начнётся всё с завоевания серверного рынка, для которого DDR5 преподнесёт возможность расширить банки памяти и увеличить скорость передачи данных от модулей к процессорам и обратно. Согласно требованиям черновой редакции стандарта DDR5, питание чипов снижено с 1,2 В до 1,1 В, что обещает снизить потребление памяти на 30 % по сравнению с памятью DDR4. При этом скорость обмена выросла на 60 % или до 5200 Мбит/с, если сравнивать с одной из быстрейших сегодня памятью DDR4-3200. Совокупно скорость обмена с модулем памяти DDR5 вырастет до 41,6 Гбайт/с — это 11 фильмов с качеством Full HD, переданных за 1 секунду, каждый из которых будет «весить» 3,7 Гбайт. Традиционно нелепый пример, да, но даёт представление о масштабах изменений. Столь быстрая память, уверены в компании, придаст новый импульс развитию платформ ИИ, машинного обучения и работам с массивами данных.  Для снижения ошибок чтения разработчикам пришлось внести много изменений в схемотехнику памяти. Кстати, сигнальные интерфейсы пришлось доработать также по той причине, что модули памяти DDR5 будут использовать вдвое больше банков (32 вместо 16), чем память DDR4. Это также потребовало вести согласованные работы с производителями модулей RDIMM (Registered Dual In-line Memory Module) и UDIMM (Unbuffered DIMM) для серверных платформ. Также компания заявляет, что механизмы коррекции ECC теперь встроены в чипы памяти. Всё надёжнее и надёжнее, что вызвано также увеличением скорости обмена. Ранее в этом году Cadence и Micron провели первую в отрасли публичную демонстрацию работы оперативной памяти (dynamic random access memory, DRAM) следующего поколения — DDR5. На мероприятии TSMC в начале этого месяца компании представили дополнительную информацию как о стандарте в целом, так и о разработке решений на его базе. Оказывается, окончательная спецификация DDR5 ещё не была принята JEDEC, но Micron всё ещё планирует начать производство чипов памяти DDR5 в конце 2019 года. Как отмечалось ещё в мае, основной особенностью DDR5 SDRAM является увеличенная ёмкость микросхем, а не только более высокая производительность и низкое энергопотребление. Разумеется, DDR5 обеспечит скорость работы интерфейса от 4266 до 6400 МТрансферов/с, её напряжение питания снизится до 1,1 В с допустимым диапазоном колебаний 3 % (т. e. на ± 0,033 В) и будет использовать два независимых 32/40-разрядных канала на модуль (без/или с ECC). Кроме того, DDR5 увеличит эффективность командной шины (поскольку оба независимых канала будут иметь свою собственную 7-разрядную шину адресов (Add) и команд (Cmd)), получит лучшие схемы обновления, а также увеличенное количество групп банков для дополнительного увеличения производительности. Примечательно, что в Cadence говорят о том, что технологические усовершенствования DDR5 позволят увеличить реальную пропускную способность памяти на 36 % по сравнении с DDR4 даже при скорости передачи данных 3200 МТ/с, а после того, как DDR5 заработает на проектных скоростях вроде 4800 МТ/с, фактическая пропускная способность станет на 87 % выше, чем у DDR4-3200 (другой вопрос, какие при этом будут задержки). Тем не менее, одной из ключевых особенностей DDR5 станет именно возможность увеличивать плотность монолитной микросхемы памяти свыше 16 Гбит.  Прототип контроллера памяти компании Cadence Ведущие производители оперативной памяти уже имеют в своём арсенале монолитные чипы DDR4 ёмкостью 16 Гбит, но эти устройства не могут предложить действительно высоких тактовых частот или скоростей ввода/вывода из-за законов физики. По этой причине компаниям вроде Micron предстоит проделать немалую работу, чтобы объединить высокую производительность и плотность ячеек DRAM. В частности, в Micron обеспокоены непостоянным временем удержания заряда ячейками памяти, а также другими феноменами на уровне атомов для микросхем памяти, произведённых по технологическим процессам 10–12 нм. При этом в случае с DDR5 шина Add/Cmd уже имеет встроенную терминацию, призванную сделать сигналы более чистыми и увеличить стабильность при высоких скоростях передачи данных. Кроме того, модули памяти высокой ёмкости будут экипироваться собственными регуляторами напряжения и управления питания. Таким образом, хотя стандарт DDR5 и адаптирован к тому, чтобы объединить производительность и плотность, компаниям вроде Micron потребуется проявить своё мастерство при изготовлении соответствующих микросхем.  Микросхемы памяти DDR5 производства Micron Micron рассчитывает начать производство чипов памяти DDR5 ёмкостью 16 Гбит с использованием техпроцесса с «шириной затвора менее 18 нм» уже в конце 2019 года. Впрочем, это не означает, что одновременно с этим появятся приложения, использующие новую DRAM. В свою очередь, Cadence уже предлагает готовый блок DDR5 (контроллер + физический интерфейс), реализованный для техпроцессов TSMC N7 (7 nm, DUV) и N7+ (7 nm, DUV+EUV). Таким образом, у разработчиков систем на кристалле (system-on-chip, SoC) есть всё необходимое для создания совместимых с новым типом памяти SoC. Кроме того, в Cadence работают над соответствующими IP-блоками DDR5 и для более совершенных норм производства.  Предположения Cadence в области принятия DDR5 различными типами устройств Учитывая ключевые преимущества DDR5, неудивительно, что серверы станут первыми устройствами, использующими новый тип оперативной памяти, согласно ожиданиям Cadence. Что особенно интересно, так это то, что в Cadence полагают, что SoC для клиентских компьютеров, произведенные по техпроцессу N7+, будут поддерживать DDR5. По сути, это означает, что подобные процессоры начнут появляться уже в 2020 году. Учитывая предсказываемые Cadence высокие темпы принятия DDR5 рынком, логично предполагать, что новый тип оперативной памяти будет поддержан широким спектром SoC.  Тенденции на рынке оперативной памяти по оценкам Cadence 07.05.2018 [09:01], Иван ГрудцынВывод на рынок оперативной памяти нового поколения — DDR5 — ожидается в следующем году, после того как летом JEDEC утвердит финальную спецификацию соответствующего стандарта, а разработчики и производители RAM предоставят клиентам микросхемы и контроллеры DDR5. Подготовка к серии релизов ведётся непрерывно. Компания Cadence, желая продемонстрировать успехи в работе с оперативной памятью нового поколения, показала прототип устройства DDR5-4400. В его основу легли 7-нм микроконтроллер Cadence и 8-Гбит чипы Micron DDR5.  Получившийся у Cadence прототип напоминает что угодно, кроме модуля оперативной памяти, тем не менее компактное исполнение решений DDR5 в целом не является проблемой.  Устройство обеспечивает передачу данных со скоростью 4400 МТ/с (DDR-4400) в сочетании с высокой CAS-латентностью (CL) — 42 такта. Впрочем, с ростом пропускной способности RAM обычно увеличиваются и тайминги. Типичные значения CAS-латентности для DDR составляли 2,5–3 такта, для DDR2 — 4–6, для DDR3/DDR3L — 9–11, для DDR4 — 15–17. Значение CL у DDR5 в 42 такта несколько удручает, но в серийных продуктах задержки могут быть снижены.  Напряжение памяти нового типа на 8,3 % ниже, чем у DDR4 — 1,1 В, допустимое отклонение составляет всего 0,033 В в большую или меньшую сторону. В JEDEC рассчитывают, что со временем DDR5 достигнет скорости передачи данных в 6400 МТ/с (DDR5-6400). В свою очередь, специалисты Cadence полагают, что на первых порах оперативная память DDR пятого поколения будет работать в режиме 4400 МТ/с из-за ограничений со стороны контроллера.  Разработчик делает акцент на том, что технология DDR5 позволит увеличить ёмкость микросхем с нынешних 4–16 Гбит (512 Мбайт — 2 Гбайт) до 16–32 Гбит (2–4 Гбайт). Соответственно, максимальный объём двустороннего модуля RAM данного типа для настольных ПК составит 64 Гбайт. Помимо этого, стоит отметить, что в DDR5 улучшены алгоритмы загрузки каналов памяти и энергосбережения, а также предусмотрена возможность интеграции контроллера напряжения. График Cadence, иллюстрирующий соотношение разных типов оперативной памяти на рынке в 2012–22 гг., указывает на то, что в эру DDR5 низковольтные чипы (LPDDR5) будут распространены больше, чем обычные. В 2019–20 гг. влияние DDR5 на рынок вычислительных устройств будет небольшим, но уже в 2021 году DDR5 и LPDDR5 сравняются по объёмам выпуска с нынешним дуэтом DDR4 и LPDDR4, а ещё через год DDR пятого поколения станет доминирующим типом оперативной памяти.  08.12.2017 [10:06],

Иван Грудцын 08.12.2017 [10:06],

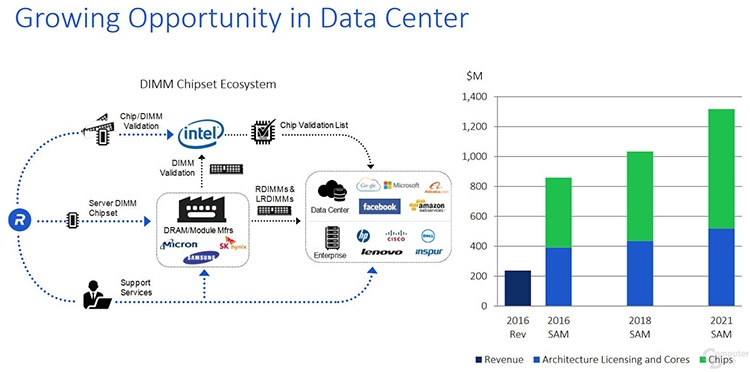

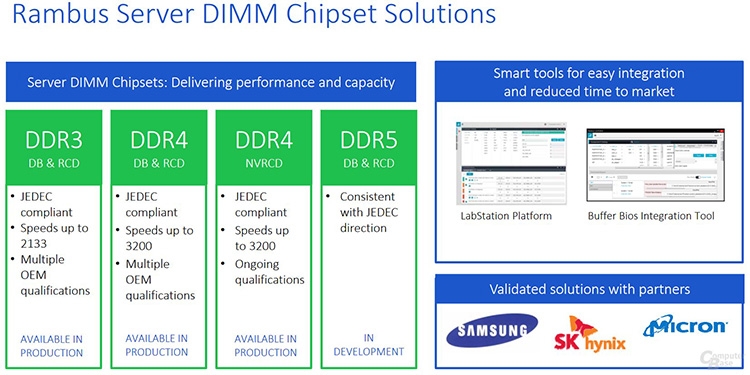

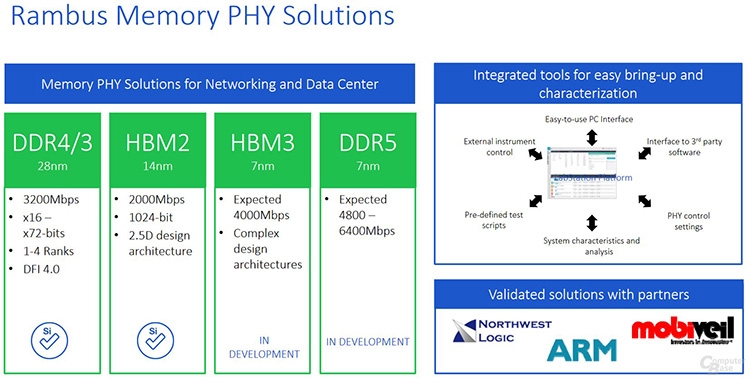

Иван ГрудцынПредставители одного из опытнейших разработчиков энергозависимой памяти — компании Rambus — на днях пообщались с инвесторами, рассмотрев как финансовые вопросы, так и планы на будущее. Rambus нередко упоминается в качестве патентного тролля, однако в компании делают акцент на участии в перспективных проектах, таких как разработка контроллеров оперативной памяти DDR5 и многослойной оперативной памяти HBM3. Последняя найдёт своё применение в готовящихся графических и HPC-ускорителях, а DDR5 со временем повсеместно заменит DDR4 — начиная с серверов и заканчивая мобильными устройствами.  Для рядового потребителя сегодня на первом плане скорее стоит вопрос стоимости оперативной памяти, нежели её пропускной способности или других характеристик. Тем не менее разработчики, и в их числе Rambus, продолжают трудиться над соответствующими контроллерами. На сегодняшний день единственным крупным клиентом Rambus является компания AMD, которая использует плод стараний соседей по Саннивейлу — контроллер DDR4 — в процессорах Ryzen.  DDR5 почти наверняка начнёт свой путь с серверного рынка, поэтому Rambus акцентирует внимание потенциальных клиентов на контроллерах DDR5 в составе модулей памяти для серверных платформ. Характерная для этих контроллеров скорость передачи данных ожидается на уровне 4800–6400 МТ/с, техпроцесс выпуска — 7 нм. Последнее обстоятельство, а также планы разработчиков оперативной памяти по выводу на рынок DDR5 только в 2020–21 гг., говорят о том, что производство вышеупомянутых контроллеров Rambus начнётся ещё не скоро.  Эффективная частота модулей DDR5 составит не менее 4800 МГц, пропускная способность — от 38,4 Гбайт/с, максимальный объём, в связи с переходом на более тонкий техпроцесс, вырастет вдвое. Рабочее напряжение, скорее всего, снизится с 1,2 В у DDR4 до 1,1 В у DDR5. Полагаем, что свой путь память DDR пятого поколения начнёт с HPC — серверов для ресурсоёмких вычислений.  Контроллеры памяти Rambus, ассоциированные с HBM3, появятся в эру 7-нм графических процессоров и будут выпускаться по той же технологической норме. Скорость передачи данных у этих контроллеров будет достигать 4000 МТ/с. Сама память HBM3 составит конкуренцию достаточно «взрослой» (к моменту покорения полупроводниковой индустрией 7-нм рубежа) графической памяти GDDR6. В отличие от массовой DDR5, память HBM3 будет больше ориентирована на конкретные проекты и продукты, в которых важна не только пропускная способность, но и компактность исполнения.  AMD Radeon R9 Nano с памятью HBM Rambus прогнозирует, что в текущем году её доход от реализации продукции всех видов составит $28 млн, а лицензионные отчисления от более чем 2500 патентов — около $212 млн. Крупнейшими «донорами» компании на сегодняшний день являются Broadcom, IBM, Intel, Micron, Qualcomm, Samsung, SK Hynix и WD.  22.09.2017 [18:25],

Сергей Карасёв 22.09.2017 [18:25],

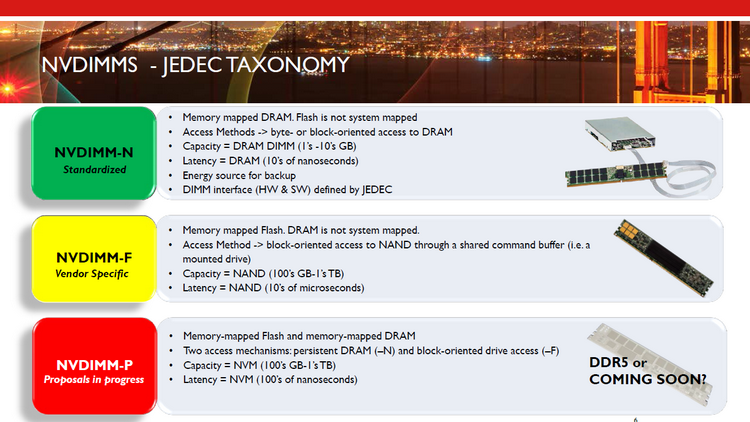

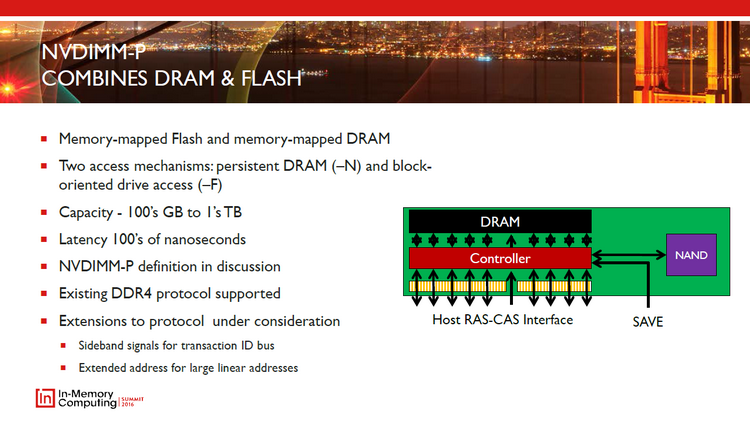

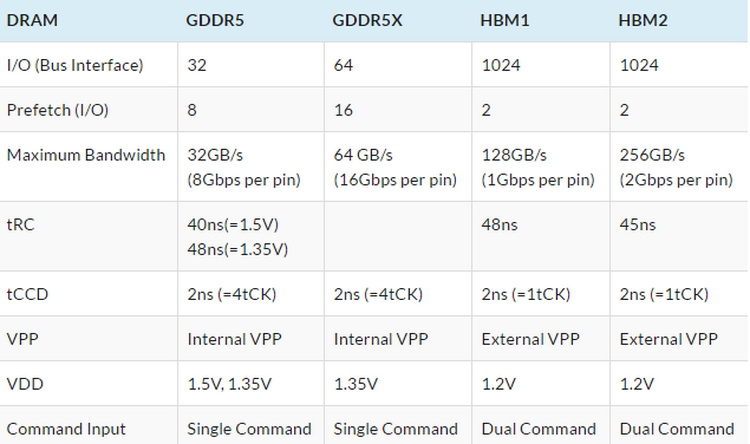

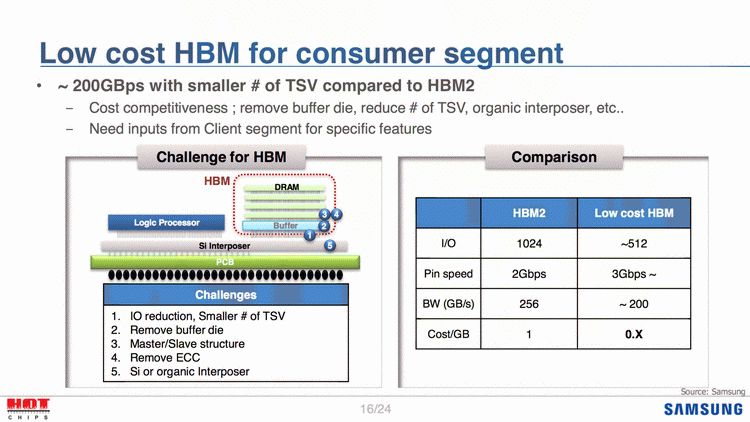

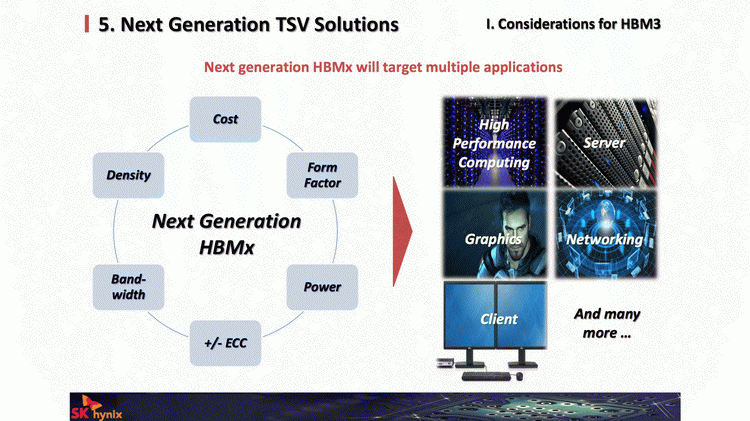

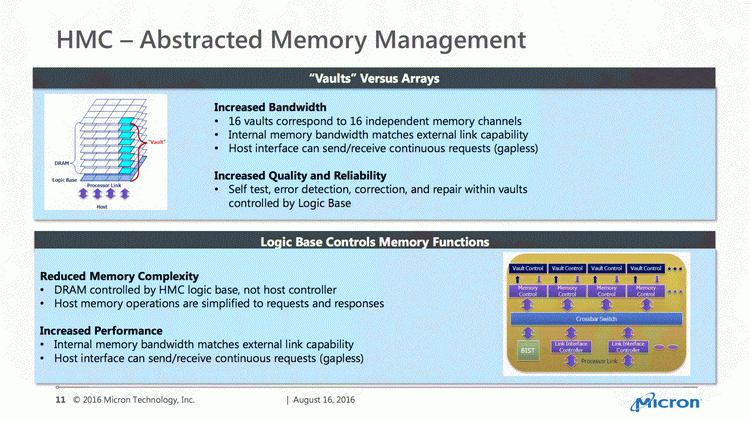

Сергей КарасёвКомпания Rambus, по сообщениям сетевых источников, уже приступила к лабораторным испытаниям модулей оперативной памяти следующего поколения.  Речь идёт о решениях DDR5 — Double Data Rate 5. Для нового стандарта заявлено «удвоение характеристик» по сравнению с нынешней памятью DDR4. Это означает, что частота составит от 4800 МГц. Скорость передачи данных — до 51,2 Гбайт/с. Помимо повышенной пропускной способности, память нового поколения предложит дальнейшие улучшения в плане энергопотребления. Благодаря более высокой плотности микрочипов вырастет ёмкость модулей. Комитет инженерной стандартизации полупроводниковой продукции (JEDEC) рассчитывает обнародовать финальную спецификацию DDR5 уже в следующем году.  В Rambus заявляют, что компания одной из первых приступила к лабораторным тестам рабочих микросхем памяти DDR5 DIMM. Производство таких изделий, как ожидается, будет налажено ориентировочно в 2019 году. На первых порах оперативная память DDR5 появится в серверах и настольных игровых системах топового уровня. Затем она выйдет на массовый рынок персональных компьютеров и ноутбуков. 06.04.2017 [11:46], Алексей СтепинСовсем недавно мы писали о том, что комитет инженерной стандартизации полупроводниковой продукции (JEDEC), в числе прочего ответственный за разработку спецификаций новых поколений полупроводниковой памяти DRAM, планирует завершить подготовку стандарта DDR5 в 2018 году. Но DDR5 — это не просто более высокая скорость передачи данных в сравнении с DDR4, основным стандартом оперативной памяти сейчас. Это ещё и ряд новых технологий на стыке DRAM и энергонезависимой памяти; такое сочетание уже получило устоявшееся название NVDIMM, хотя текущие реализации далеки от идеала.  Технически объявленное «удвоение характеристик» означает создание чипов DDR5 ёмкостью 32 Гбит со скоростью передачи данных 4266‒6400 мегатранзакций в секунду на контакт. Если модули DDR5 сохранят разрядность шины 64 бита на модуль, это означает появление односторонних модулей DDR5-6400 ёмкостью 32 Гбайт со скоростью передачи данных 51,2 Гбайт/с. «Дружественный пользователю интерфейс» может означать новую, более удобную систему фиксации модуля в системной плате. На сегодня в этом плане сложно придумать что-то действительно новое, но, возможно, инженерам JEDEC удастся всех удивить.  JEDEC обещает решить и проблему падения эффективности подсистем памяти, которая в пересчёте на канал падает по мере увеличения количества каналов, но пока не известно, как именно это будет сделано. Более подробная информация ожидается на мероприятии Server Forum, которое состоится в Санта-Кларе, штат Калифорния, США, и начнётся 19 июня. В числе планируемых к 2018 году стандартов относится и новое поколение энергонезависимых модулей памяти NVDIMM-P, которое не будет ограничено объёмом, диктуемым технологиями DRAM. Ёмкость таких модулей может достигать единиц терабайт, но при этом в жертву приносится латентность, составляющая сотни наносекунд. 31.03.2017 [10:40], Сергей КарасёвКомитет инженерной стандартизации полупроводниковой продукции (JEDEC) сообщил о том, что разработка стандарта оперативной памяти DDR5 (Double Data Rate 5) быстро продвигается вперёд.  Память DDR5 по сравнению с предыдущими реализациями предложит ряд преимуществ. Благодаря вдвое более высокой плотности микрочипов вырастет ёмкость модулей, а следовательно, увеличится объём ОЗУ в компьютерах и серверах. Отмечается, что по сравнению с нынешней памятью DDR4 решения следующего поколения предложат в два раза более высокую пропускную способность. Кроме того, повысится энергетическая эффективность. Сетевые источники добавляют, что поначалу память DDR5 появится в серверах и настольных игровых системах класса high-end. Затем она выйдет на массовый рынок ПК и ноутбуков.  В JEDEC сообщили, что подробности о новом стандарте будут раскрыты 19 июня нынешнего года на специальном мероприятии в Санта-Кларе (Калифорния, США). Публикация финальной спецификации DDR5 намечена на 2018 год. Ожидается, что постепенный переход от DDR4 на память нового поколения начнётся только в конце текущего десятилетия — ориентировочно в 2020 году. 23.08.2016 [15:00], Алексей СтепинВ последние пару лет полупроводниковая промышленность совершила большой скачок в области технологий производства памяти. Классическая DRAM в том или ином виде с нами уже не один десяток лет, но выход новых устройств, нуждающихся в огромных скоростях передачи данных, вызвал появление на свет совершенно нового типа памяти — HBM. Впервые она была опробована компанией AMD в графическом процессоре Fiji, который стал основой видеокарт Radeon R9 Fury X, Fury и Nano, а также Radeon Pro Duo.  Даже в самой первой инкарнации четыре сборки HBM смогли обеспечить пропускную способность на уровне 512 Гбайт/с, чего сегодня не может даже новейший NVIDIA TITAN X с 384-битной памятью GDDR5X (480 Гбайт/с). Спустя год Samsung удалось в достаточной мере нарастить объёмы производства новой версии многослойной высокоскоростной памяти HBM2, которая нашла своё применение в вычислительных ускорителях NVIDIA Tesla P100. Они уже поставляются на рынок супервычислений и облачных систем начиная со второго квартала текущего года.  Уже становится очевидным, что обычная DRAM хотя и просуществует на рынке достаточно долго, будущее принадлежит многослойной памяти — HBM и другим аналогичным технологиям. К тому же HBM располагается на упаковке рядом с ЦП или ГП и не требует много места, что позволяет сделать системы с её использованием более компактными. Но HBM2 пока новый, дорогой продукт, выпускающийся в недостаточно массовых количествах. Мы знаем, что производство HBM2 Samsung начала в первом квартале этого года, а SK Hynix запаздывает и только собирается начать выпуск своего варианта HBM2 в этом квартале.  На мероприятии Hot Chips 28 обе компании продемонстрировали свои каталоги выпускаемых продуктов и планы на будущее относительно многослойной памяти. Согласно опубликованным слайдам, у HBM2 есть как минимум две альтернативы или ответвления — HBM3 и low cost HBM. Последняя представляет особенный интерес. Эта удешевлённая версия HBM была представлена Samsung как выгодное по цене решение, опережающее HBM1, но несколько уступающее в производительности HBM2. Удешевление достигнуто за счёт уменьшения с 1024 до 512 количества пронизывающих сборку кристаллов TSV — соединений, с помощью которых кристаллы HBM и общаются с внешним миром.  В результате получается память, способная обеспечивать скорость 3 Гбайт/с на контакт и 200 Гбайт/с на сборку против 256 Гбайт/с на сборку у полноценной HBM2. 512-битный интерфейс доступа с двумя или четырьмя сборками означает 1024 или 2048 Мбайт. Samsung утверждает, что она может легко производить такие чипы в массовых количествах и наводнить ими рынок. В то же время, когда HBM2 ещё не успела завоевать рынка, обе компании — Samsung и SK Hynix — уже готовятся к разработке и выпуску следующего поколения многослойной памяти, так называемой xHBM или HBM3. Первое название характерно для Samsung, второе используется SK Hynix.  Характеристики нового стандарта ещё далеки от финализации, но ключевые моменты новой технологии были оглашены. HBM3 обеспечит вдвое более высокую пропускную способность и будет обладать привлекательной ценой. Речь идёт о скоростях порядка 512 Гбайт/с на сборку против 256 Гбайт/с у HBM2. Четыре таких кристалла легко смогут обеспечить пропускную способность на уровне 2 Тбайт/с. Но в работе такие цифры мы увидим нескоро; коллеги с WCCFTech полагают, что речь идёт о видеокартах, которые появятся как минимум после NVIDIA Volta.  Производители памяти продолжают обсуждать такие параметры HBM3, как себестоимость, форм-факторы, энергопотребление и плотность упаковки. Сейчас HBM2 может обеспечить ёмкость до 48 Гбайт, так что с внедрением HBM3 следует ожидать цифр от 64 Гбайт. Но не одной HBM жива индустрия памяти. Как уже было сказано, DRAM ещё долго будет присутствовать на рынке, и компания Micron огласила свои планы в отношении этого типа памяти.  Планируется, что опытные поставки чипов DDR5 DRAM начнутся в 2018 году, а массовое производство таких микросхем (и модулей памяти) развернётся годом позже, в 2019 г. Ключевой особенностью DDR5 в сравнении с DDR4 является вдвое более высокая пропускная способность и напряжение питания, составляющее всего 1,1 вольта. Это означает повышение тактовых частот, а ёмкость будет варьироваться в пределах от 8 до 32 Гбайт. Эквивалентные частоты для DDR5 составят 3200 МГц в начале производства и достигнут значения 6400 МГц по мере того, как выход годных кристаллов будет увеличиваться, а новый стандарт — завоевывать рынок оперативной памяти.  Micron также рассказала о своей альтернативе HBM, многослойной памяти HMC (Hybrid Memory Cube). Компания называет HBM «плохой копией» HMC, поскольку последняя обладает рядом возможностей, недоступных HBM и может состязаться с ней только в пропускной способности. Помимо всего прочего, Micron продолжает активно сотрудничать с Intel в разработке и продвижении энергонезависимой памяти нового поколения 3D XPoint. Подводя итоги, скажем, что ключевыми годами для рынка памяти, основываясь на имеющихся данных, можно назвать 2018-й и 2019-й. 19.08.2016 [18:37], Сергей КарасёвВ ходе Форума Intel для разработчиков (IDF 2016) была обнародована информация об ориентировочных сроках внедрения оперативной памяти следующего поколения — DDR5.  Сообщается, что спецификация DDR5 будет опубликована уже до конца текущего года. Однако постепенный переход от DDR4 на память нового поколения начнётся только в конце текущего десятилетия — ориентировочно в 2020 году. Память DDR5 по сравнению с предыдущими реализациями предложит ряд преимуществ. Благодаря более высокой плотности микрочипов вырастет ёмкость модулей, а следовательно, увеличится объём ОЗУ в компьютерах и серверах.  Говорится о повышении производительности при одновременном снижении энергопотребления. Таким образом, вырастет быстродействие конечных устройств, а также время автономной работы ноутбуков от аккумуляторных батарей. Ожидается, что поначалу внедрение DDR5 начнётся в серверном сегменте. Настольные компьютеры и ноутбуки станут комплектоваться памятью нового поколения на 12–18 месяцев позднее. Использоваться память DDR5, по мнению экспертов, будет как минимум до 2025 года. |

Cadence показала прототип DDR5-4400

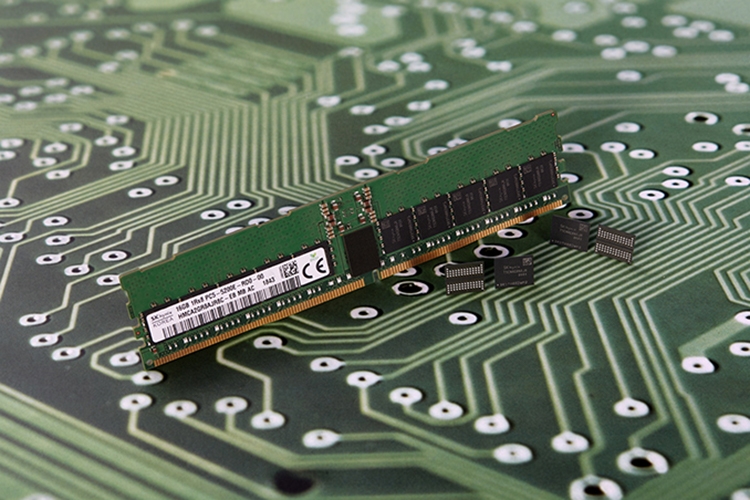

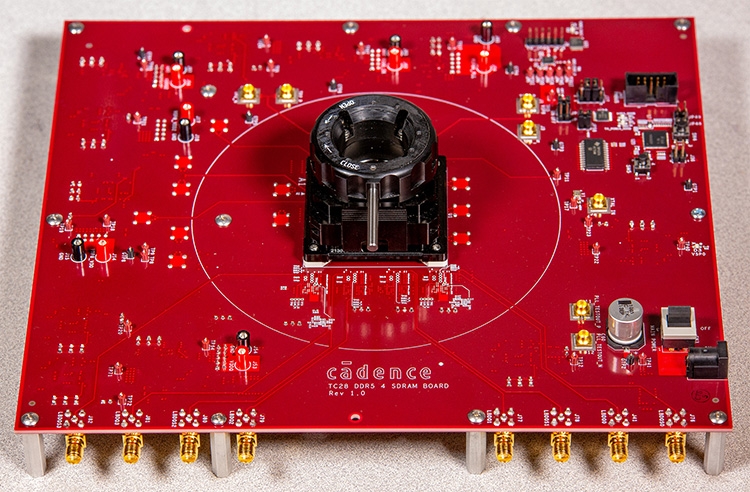

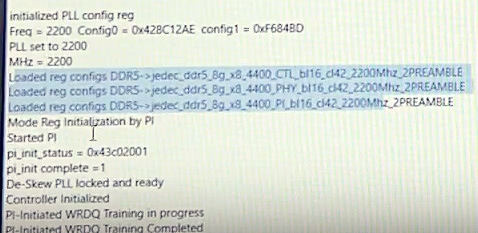

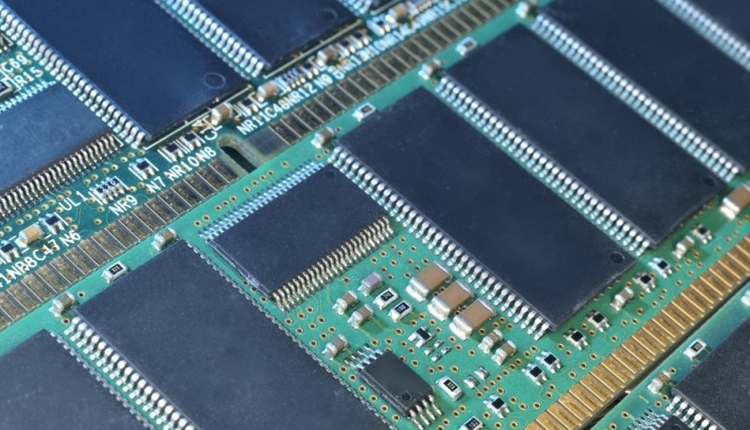

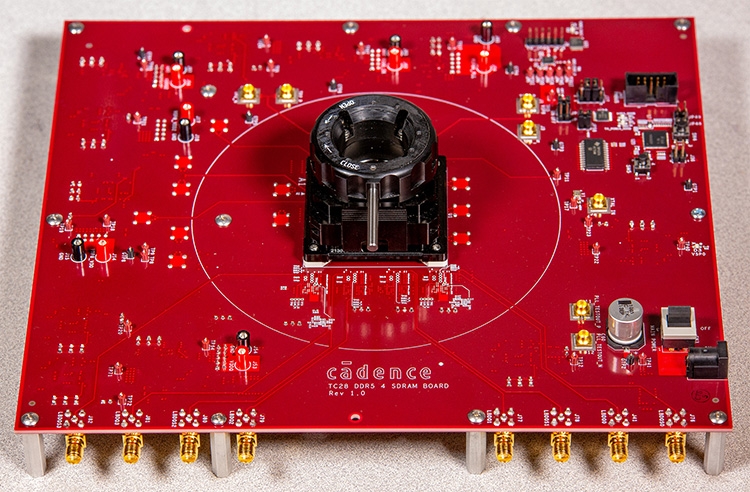

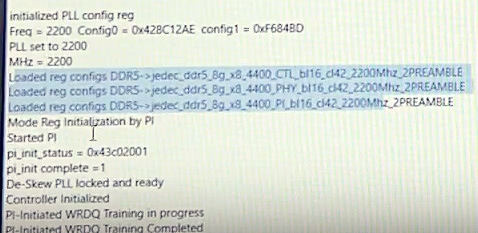

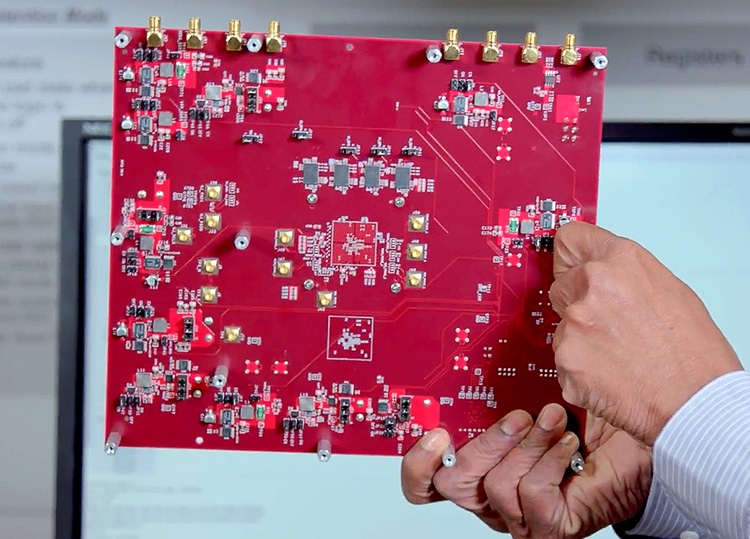

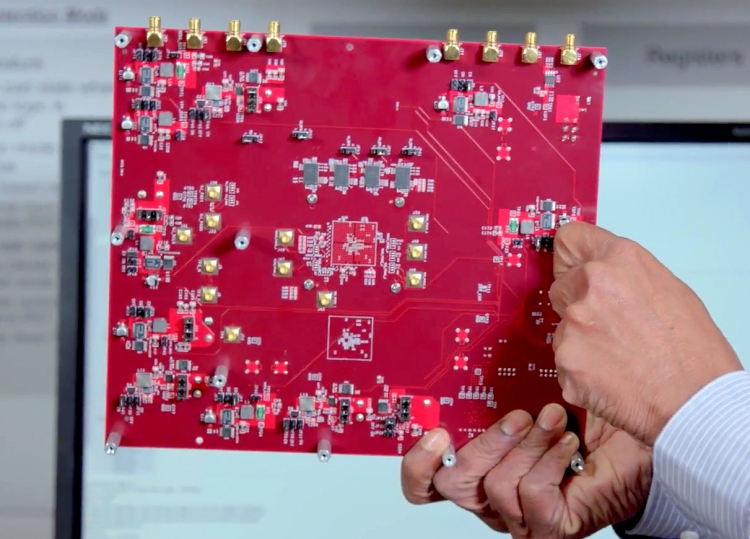

Вывод на рынок оперативной памяти нового поколения — DDR5 — ожидается в следующем году, после того как летом JEDEC утвердит финальную спецификацию соответствующего стандарта, а разработчики и производители RAM предоставят клиентам микросхемы и контроллеры DDR5. Подготовка к серии релизов ведётся непрерывно. Компания Cadence, желая продемонстрировать успехи в работе с оперативной памятью нового поколения, показала прототип устройства DDR5-4400. В его основу легли 7-нм микроконтроллер Cadence и 8-Гбит чипы Micron DDR5.

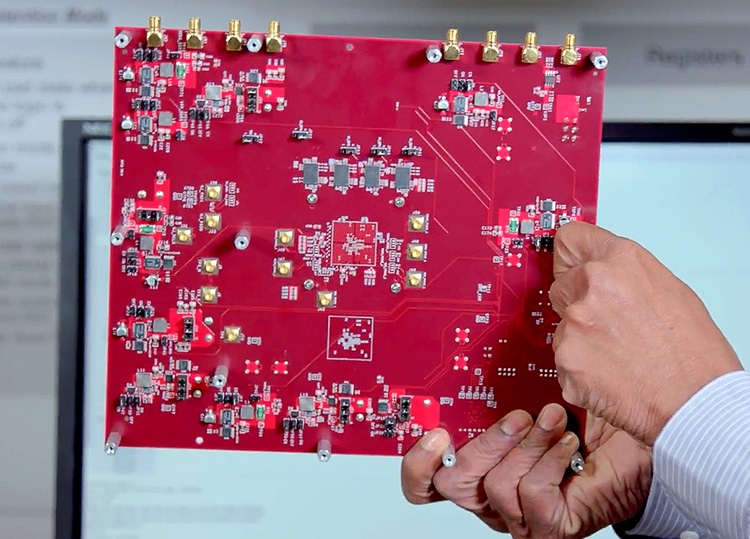

Получившийся у Cadence прототип напоминает что угодно, кроме модуля оперативной памяти, тем не менее компактное исполнение решений DDR5 в целом не является проблемой.

Устройство обеспечивает передачу данных со скоростью 4400 МТ/с (DDR-4400) в сочетании с высокой CAS-латентностью (CL) — 42 такта. Впрочем, с ростом пропускной способности RAM обычно увеличиваются и тайминги. Типичные значения CAS-латентности для DDR составляли 2,5–3 такта, для DDR2 — 4–6, для DDR3/DDR3L — 9–11, для DDR4 — 15–17. Значение CL у DDR5 в 42 такта несколько удручает, но в серийных продуктах задержки могут быть снижены.

Напряжение памяти нового типа на 8,3 % ниже, чем у DDR4 — 1,1 В, допустимое отклонение составляет всего 0,033 В в большую или меньшую сторону. В JEDEC рассчитывают, что со временем DDR5 достигнет скорости передачи данных в 6400 МТ/с (DDR5-6400). В свою очередь, специалисты Cadence полагают, что на первых порах оперативная память DDR пятого поколения будет работать в режиме 4400 МТ/с из-за ограничений со стороны контроллера.

Разработчик делает акцент на том, что технология DDR5 позволит увеличить ёмкость микросхем с нынешних 4–16 Гбит (512 Мбайт — 2 Гбайт) до 16–32 Гбит (2–4 Гбайт). Соответственно, максимальный объём двустороннего модуля RAM данного типа для настольных ПК составит 64 Гбайт. Помимо этого, стоит отметить, что в DDR5 улучшены алгоритмы загрузки каналов памяти и энергосбережения, а также предусмотрена возможность интеграции контроллера напряжения.

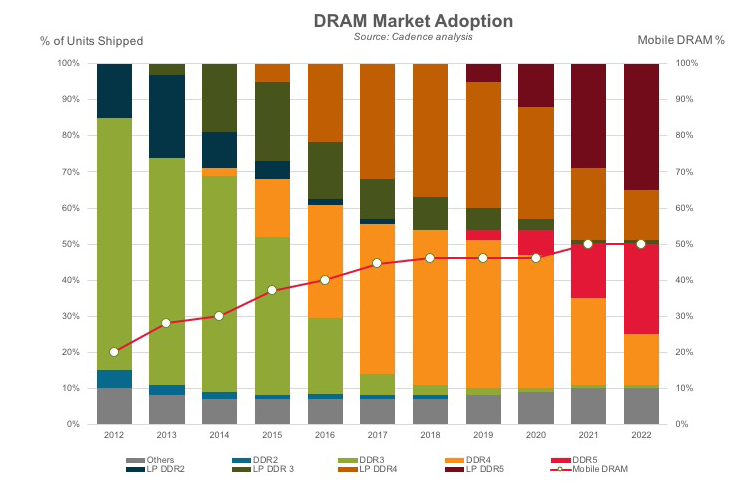

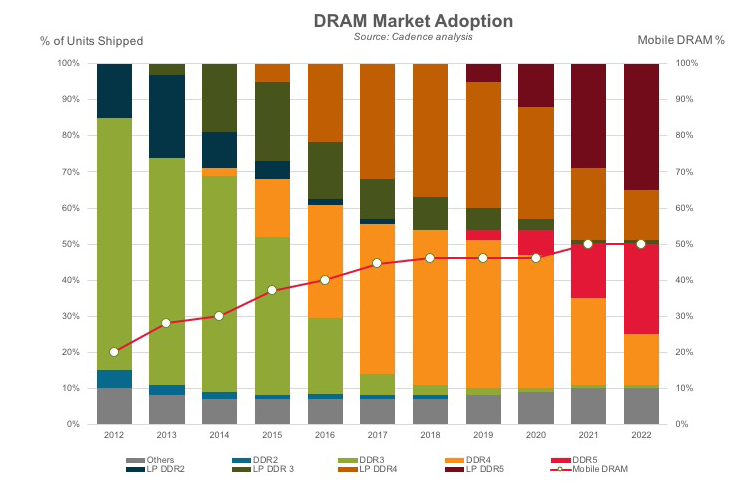

График Cadence, иллюстрирующий соотношение разных типов оперативной памяти на рынке в 2012–22 гг., указывает на то, что в эру DDR5 низковольтные чипы (LPDDR5) будут распространены больше, чем обычные. В 2019–20 гг. влияние DDR5 на рынок вычислительных устройств будет небольшим, но уже в 2021 году DDR5 и LPDDR5 сравняются по объёмам выпуска с нынешним дуэтом DDR4 и LPDDR4, а ещё через год DDR пятого поколения станет доминирующим типом оперативной памяти.

Если вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

16-Гбит чипы появятся в 2019 году

Ранее в этом году Cadence и Micron провели первую в отрасли публичную демонстрацию работы оперативной памяти (dynamic random access memory, DRAM) следующего поколения — DDR5. На мероприятии TSMC в начале этого месяца компании представили дополнительную информацию как о стандарте в целом, так и о разработке решений на его базе. Оказывается, окончательная спецификация DDR5 ещё не была принята JEDEC, но Micron всё ещё планирует начать производство чипов памяти DDR5 в конце 2019 года.

Как отмечалось ещё в мае, основной особенностью DDR5 SDRAM является увеличенная ёмкость микросхем, а не только более высокая производительность и низкое энергопотребление. Разумеется, DDR5 обеспечит скорость работы интерфейса от 4266 до 6400 МТрансферов/с, её напряжение питания снизится до 1,1 В с допустимым диапазоном колебаний 3 % (т. e. на ± 0,033 В) и будет использовать два независимых 32/40-разрядных канала на модуль (без/или с ECC). Кроме того, DDR5 увеличит эффективность командной шины (поскольку оба независимых канала будут иметь свою собственную 7-разрядную шину адресов (Add) и команд (Cmd)), получит лучшие схемы обновления, а также увеличенное количество групп банков для дополнительного увеличения производительности. Примечательно, что в Cadence говорят о том, что технологические усовершенствования DDR5 позволят увеличить реальную пропускную способность памяти на 36 % по сравнении с DDR4 даже при скорости передачи данных 3200 МТ/с, а после того, как DDR5 заработает на проектных скоростях вроде 4800 МТ/с, фактическая пропускная способность станет на 87 % выше, чем у DDR4-3200 (другой вопрос, какие при этом будут задержки). Тем не менее, одной из ключевых особенностей DDR5 станет именно возможность увеличивать плотность монолитной микросхемы памяти свыше 16 Гбит.

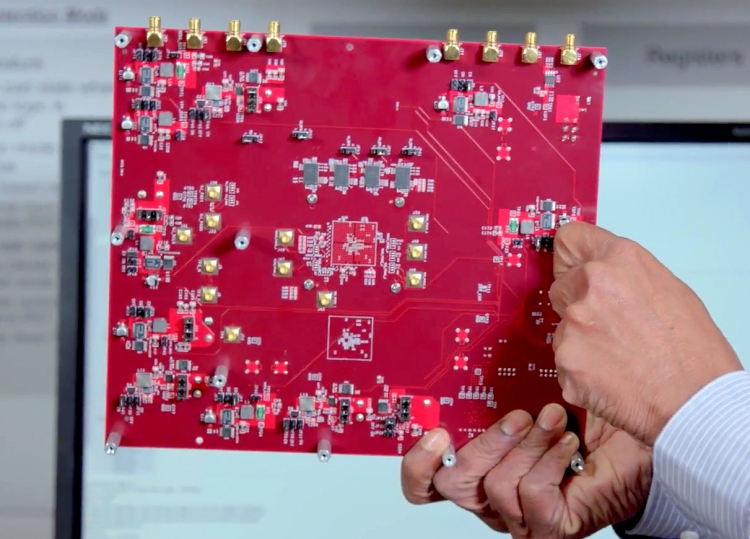

Прототип контроллера памяти компании Cadence

Ведущие производители оперативной памяти уже имеют в своём арсенале монолитные чипы DDR4 ёмкостью 16 Гбит, но эти устройства не могут предложить действительно высоких тактовых частот или скоростей ввода/вывода из-за законов физики. По этой причине компаниям вроде Micron предстоит проделать немалую работу, чтобы объединить высокую производительность и плотность ячеек DRAM. В частности, в Micron обеспокоены непостоянным временем удержания заряда ячейками памяти, а также другими феноменами на уровне атомов для микросхем памяти, произведённых по технологическим процессам 10–12 нм. При этом в случае с DDR5 шина Add/Cmd уже имеет встроенную терминацию, призванную сделать сигналы более чистыми и увеличить стабильность при высоких скоростях передачи данных. Кроме того, модули памяти высокой ёмкости будут экипироваться собственными регуляторами напряжения и управления питания. Таким образом, хотя стандарт DDR5 и адаптирован к тому, чтобы объединить производительность и плотность, компаниям вроде Micron потребуется проявить своё мастерство при изготовлении соответствующих микросхем.

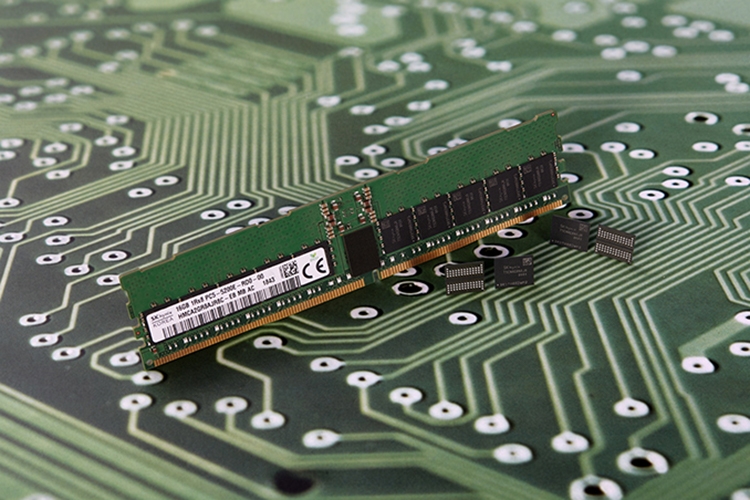

Микросхемы памяти DDR5 производства Micron

Micron рассчитывает начать производство чипов памяти DDR5 ёмкостью 16 Гбит с использованием техпроцесса с «шириной затвора менее 18 нм» уже в конце 2019 года. Впрочем, это не означает, что одновременно с этим появятся приложения, использующие новую DRAM. В свою очередь, Cadence уже предлагает готовый блок DDR5 (контроллер + физический интерфейс), реализованный для техпроцессов TSMC N7 (7 nm, DUV) и N7+ (7 nm, DUV+EUV). Таким образом, у разработчиков систем на кристалле (system-on-chip, SoC) есть всё необходимое для создания совместимых с новым типом памяти SoC. Кроме того, в Cadence работают над соответствующими IP-блоками DDR5 и для более совершенных норм производства.

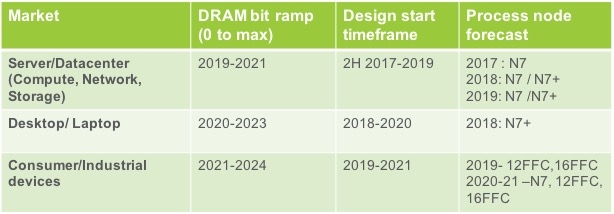

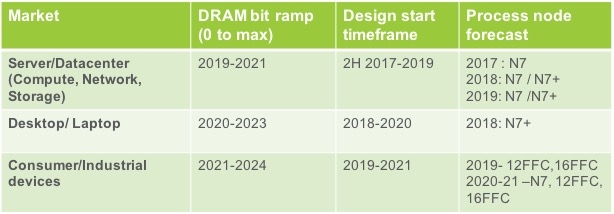

Предположения Cadence в области принятия DDR5 различными типами устройств

Учитывая ключевые преимущества DDR5, неудивительно, что серверы станут первыми устройствами, использующими новый тип оперативной памяти, согласно ожиданиям Cadence. Что особенно интересно, так это то, что в Cadence полагают, что SoC для клиентских компьютеров, произведенные по техпроцессу N7+, будут поддерживать DDR5. По сути, это означает, что подобные процессоры начнут появляться уже в 2020 году. Учитывая предсказываемые Cadence высокие темпы принятия DDR5 рынком, логично предполагать, что новый тип оперативной памяти будет поддержан широким спектром SoC.

Тенденции на рынке оперативной памяти по оценкам Cadence

Если вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.

Micron начинает подготовку к производству DDR5 памяти — PC-01

Компания производит чипы памяти для серверных ECC DIMM модулей на 1znm техпроцессе.

В текущий момент не идёт речь о массовом производстве памяти. Micron заявляет, что память нового типа может принести рост производительность до 85% в некоторых серверных задачах в сравнении с DDR4 (имея ввиду базовые частоты).

Базовая скорость работы DDR5 будет 3200 МТ/с, JEDEC разработали ряд стандартов для DDR5 вплоть до 6400 МТ/с которая обеспечит пропускную способность памяти (ПСП) ~300 ГБ/с на канал.

Изменения протокола передачи данных также позволяют при равной скорости обмена увеличить ПСП для DDR5 в сравнении с DDR4 до 1,36 раза.

Основной упор в презентационных материалах делается на необходимость роста ПСП для многоядерных процессоров в которых удельная пропускная способность на ядро сильно упала из-за резкого роста числа ядер при неизменном стандарте DDR4.

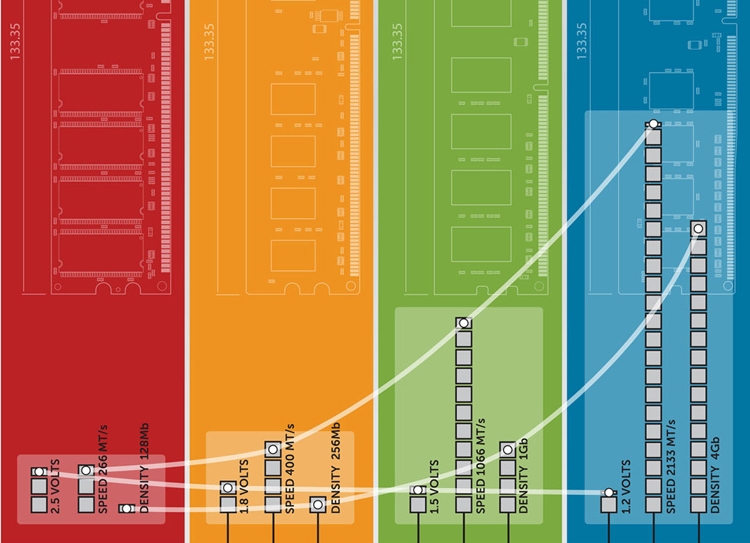

| Тип памяти | Год появления | ПСП | кол-во контактов | Напряжение (V) | Очередь операций |

|---|---|---|---|---|---|

| SDR | 1993 | 1.6 GB/s | 168 | 3.3 | 1n |

| DDR | 2000 | 3.2 GB/s | 184 | 2.5/2.6 | 2n |

| DDR2 | 2003 | 8.5 GB/s | 240 | 1.8 | 4n |

| DDR3 | 2007 | 17 GB/s | 240 | 1.35/1.5 | 8n |

| DDR4 | 2014 | 25.6 GB/s | 380 | 1.2 | 8n |

| DDR5 | 2019 | 32GB/s | 380 | 1.1 | 8/16n |

Новая память будет работать на меньших напряжениях в сравнении с DDR4 и будет существенно более энергоэффективной.

Базовое напряжение для DDR5 будет 1,1 Вольта, против 1,2 у DDR4.

В серверном сегменте ожидается появление первых устройств intel поддерживающих DDR5 в 2021 году. Также на 2021 год имеются планы на выход DDR5 совместимых устройств у китайской компании Zhaoxin.

Несмотря на отсутствие устройств поддерживающих DDR5 сама память нужна для предсерийной отработки будущих решений различных компаний, и судя по всему работы у разных производителей дошли до тех этапов когда уже необходимо наличие памяти DDR5.

Если вы нашли ошибку, пожалуйста, выделите фрагмент текста и нажмите Ctrl+Enter.

Видео на YouTube канале «Этот компьютер»

Устаревание видеокарт NVIDIA vs AMD Radeon

AMD RADEON | Драйвера 2016 vs 2020 | RX 470

Intel, AMD и Nvidia на CES 2020

Уточнение к видео про VRM (про работу даблеров)

Новости канала «Этот компьютер» и важные объявления.

Железные ожидания от 2020 года

InfoCAST #027 | Весь «железный» 2019 год в одном видео

VRM. Что такое, зачем? Фазы и цепи питания.

Архитектура Intel Sunny Cove (Ice Lake)

Микроархитектура Zen2

InfoCAST #026 | threadripper | 1650 super | intel Xe

Влияние пресетов кодирования x.264 и x.265 на качество видео

DDR5 уже готова, переходим к разработке DDR6-памяти

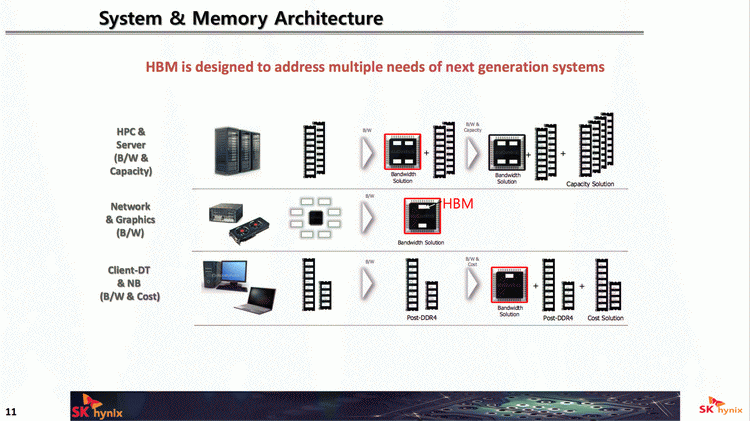

Технологии динамической памяти продолжают своё развитие. Несмотря на то, что появление DDR5 SDRAM ожидается лишь в 2020 году, некоторое время тому назад компания SK Hynix, занимающее место второго по величине производителя DRAM, приступила к разработкам следующего поколения перспективной памяти, DDR6 SDRAM. Как ожидается, такая память сможет обеспечить достижение скоростей до 12 Гбит/c на контакт. Но не стоит ждать быстрых перемен: как утверждают представители SK Hynix, разработка будет завершена в лучшем случае в течение ближайших 5–6 лет.

Более того, пока у разработчиков даже нет единого мнения о том, какую архитектуру должна получить память следующего за DDR5 поколения. «Мы обсуждаем несколько концепций пост-DDR5. Одна из них заключается в поддержании нынешней тенденции увеличения скорости передачи данных, а другая — в объединении технологий DRAM с технологиями систем на чипе», — рассказал Ким Донг-Кюн (Kim Dong-kyun), научный сотрудник по разработке DRAM в SK Hynix.

Напомним, в конце 2018 года SK Hynix объявила о завершении разработки первых чипов DDR5 SDRAM, которые работают на эффективной частоте 5200 МГц при напряжении 1,1 В. Таким образом, 16-гигабитные чипы DDR5 смогут предложить на первом этапе скорость на уровне 5,2 Гбит/с на контакт, что примерно на 60 % выше пропускной способности, обеспечиваемой DDR4 SDRAM текущего поколения. Но и это не предел, к 2022 году SK Hynix планирует довести эффективную частоту чипов DDR5 до 6400 МГц. Главная сложность в разработке DDR5 касается необходимости понизить зашумлённость полезного сигнала во время высокоскоростной передачи данных. Для решения этой проблемы внедрена технология многофазной синхронизации, а также улучшения протоколов коррекции ошибок. Ожидается, что к 2022 году чипы DDR5 SDRAM будут занимать порядка 45 % рынка.

В то же время принятие DDR6 SDRAM заведомо окажется гораздо более сложным процессом. С этим типом DRAM могут быть связаны серьёзные изменения архитектуры всей подсистемы памяти, поэтому и разработка, и последующее распространение DDR6 будет протекать заметно медленнее, чем в случае с DDR5. Кроме того, индустрия пока не пришла к единому мнению относительно того, что конкретно должна представлять собой DDR6. Иными словами, следующее за DDR5 поколение памяти представляется достаточно туманной перспективой, и сроки её появления могут отодвинуться далеко за 2024 год.

Если вы заметили ошибку — выделите ее мышью и нажмите CTRL+ENTER.